Analyse von Leistungselektronik-Designs für Hochgeschwindigkeits-SoC mit mehrphasigen Abwärtswandlern

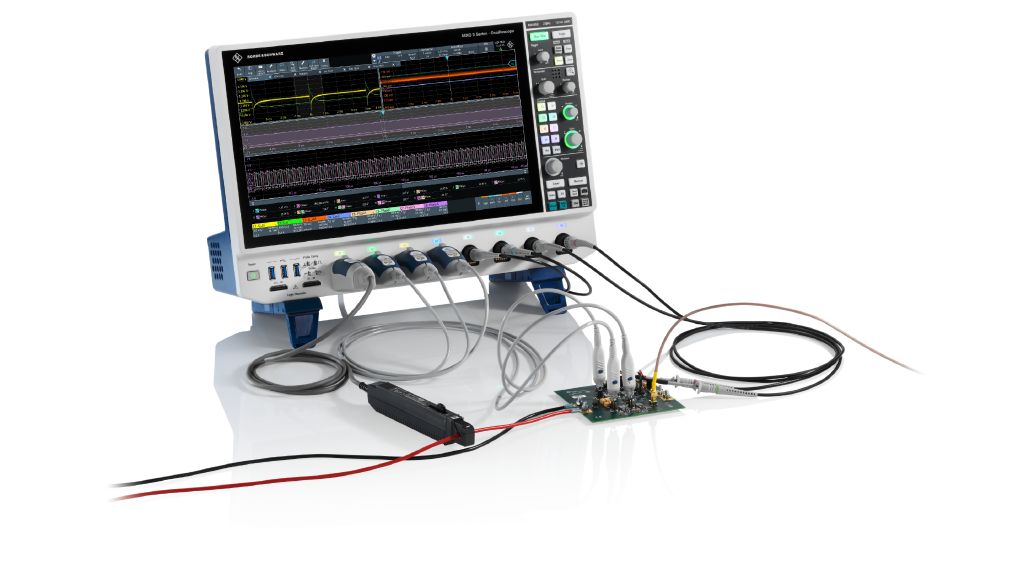

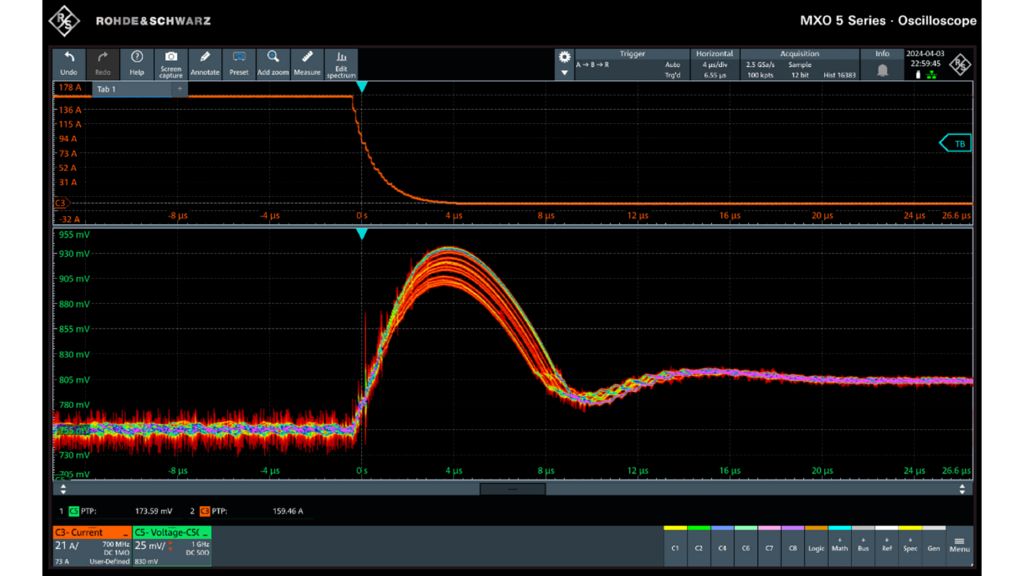

Mehr Funktionen, höhere Verarbeitungsleistungen und steigende Datenraten lassen das Leistungselektronik-Design von Hochgeschwindigkeits-SoC (System-on-Chip) zu einer Herausforderung werden. Wegen der oft großen Zahl von Stromversorgungsleitungen für die verschiedenen Funktionsblöcke moderner CPU, GPU, FPGA, ASIC usw. ist eine präzise Ein- und Ausschalt-Sequenzierung erforderlich. Im Interesse einer geringeren Verlustleistung des SoC werden zudem die Versorgungsspannungspegel klein gehalten. Es gelten strengere Anforderungen an die Leistungsintegrität, und die Stromversorgungsleitungen benötigen höhere Stromstärken. Mehrphasige Abwärtswandler gewinnen bei für hohe Ströme ausgelegten Versorgungen weiter an Beliebtheit. Diese Wandler bieten viele Vorteile. Das Leistungselektronik-Design sowie die Durchführung von Validierungstests sind jedoch mit Herausforderungen verbunden.